Product Summary

The GAL22V10C-7LJ is a High Performance E2CMOS PLD Generic Array Logic. It combines a high performance CMOS process with Electrically Erasable (E2) floating gate technology to provide the highest performance available of any 22V10 device on the market. CMOS circuitry allows the GAL22V10C-7LJ to consume much less power when compared to bipolar 22V10 devices. The applications of the GAL22V10C-7LJ are DMA Control, State Machine Control, High Speed Graphics Processing, Standard Logic Speed Upgrade.

Parametrics

GAL22V10C-7LJ absolute maximum ratings: (1)Supply voltage VCC:-0.5 to +7V; (2)Input voltage applied:-2.5 to VCC +1.0V; (3)Off-state output voltage applied:-2.5 to VCC +1.0V; (4)Storage Temperature:-65℃ to 150℃; (5)Ambient Temperature with Power Applied:-55℃ to 125℃.

Features

GAL22V10C-7LJ features: (1)4 ns Maximum Propagation Delay; (2)Fmax = 250 MHz; (3)3.5 ns Maximum from Clock Input to Data Output; (4)UltraMOS Advanced CMOS Technology; (5)Fully Function/Fuse-Map/Parametric Compatible with Bipolar and UVCMOS 22V10 Devices; (6)active pull-ups on all pins; (7)Reconfigurable Logic; (8)Reprogrammable Cells; (9)100% Tested/100% Yields; (10)High Speed Electrical Erasure (<100ms); (11)20 Year Data Retention; (12)Maximum Flexibility for Complex Logic Designs; (13)electronic signature for identification.

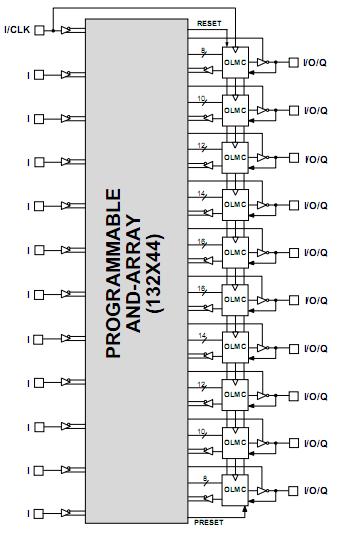

Diagrams

|

GAL20LV8 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

GAL20LV8ZD |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

GAL20RA10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

GAL20RA10B-10LJ |

Lattice |

SPLD - Simple Programmable Logic Devices 20 INPUT 10 OUTPUT 5 V LOW POWER 10ns |

Data Sheet |

Negotiable |

|

||||

|

GAL20RA10B-10LP |

Lattice |

SPLD - Simple Programmable Logic Devices 20 INPUT 10 OUTPUT 5 V LOW POWER 10ns |

Data Sheet |

Negotiable |

|

||||

|

GAL20RA10B-15LJ |

Lattice |

SPLD - Simple Programmable Logic Devices 20 INPUT 10 OUTPUT 5 V LOW POWER 15ns |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))