Product Summary

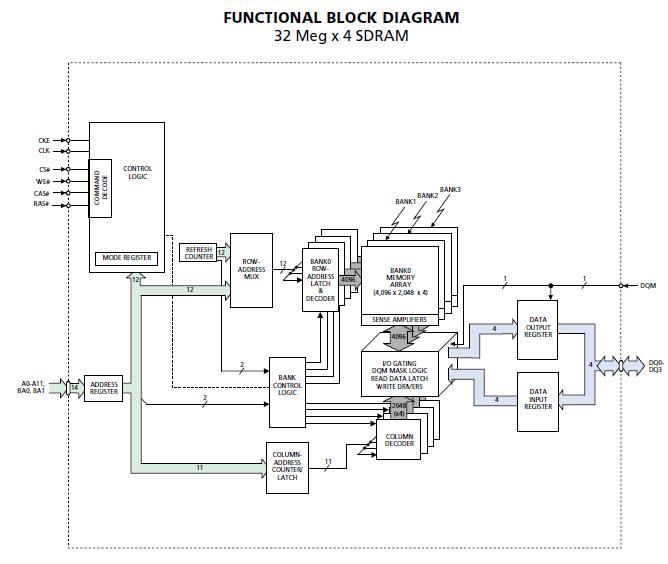

The MT48LC8M16A2TG-75 is designed as one kind of high-speed CMOS, dynamic random-access memory which containing 134,217,728 bits.It is internally configured as a quad-bank DRAM with a synchronous interface.It uses an internal pipelined architecture to achieve high-speed operation.This architecture is compatible with the 2n rule of prefetch architectures, but it also allows the column address to be changed on every clock cycle to achieve a high-speed, fully random access.

Parametrics

Absolute maximum ratings:(1)operating temperature,Ta (ambient):-1V to +4.6V;(2)storage tempera-ture (plastic):-55℃ to +150℃;(3)power dissipation:1 W.

Features

Features:(1)PC100-compliant;includes concurrent auto precharge;(2)fully synchronous, all signals registered on positive edge of system clock;(3)internal pipelined operation, column address can be changed every clock cycle;(4)internal banks for hiding row access / precharge;(5)programmable burst lengths:1,2,4,8 or full page;(6)auto precharge and auto refresh modes;(7)self refresh mode;(8)64 ms, 4,096-cycle refresh;(9)single +3.3V+/-0.3V power supply;(10)one and two clock write recovery versions.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

MT48LC8M16A2TG-75 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

MT48LC8M16A2TG-75 IT:G TR |

|

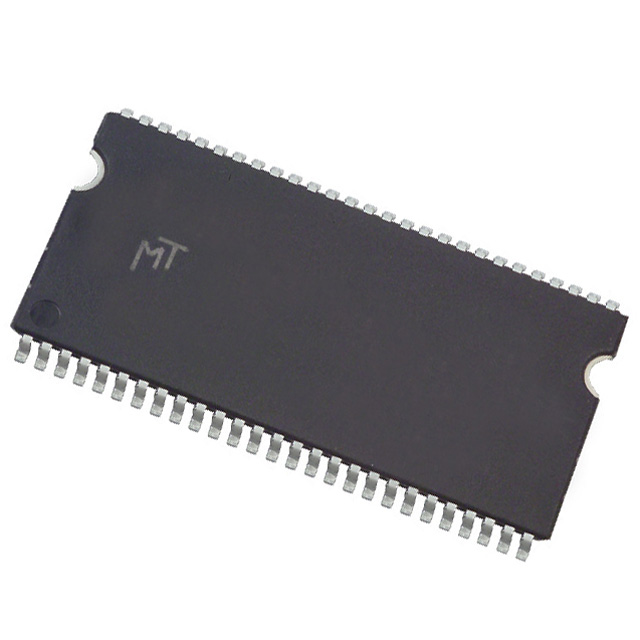

IC SDRAM 128MBIT 133MHZ 54TSOP |

Data Sheet |

|

|

||||||||||||||||||

|

MT48LC8M16A2TG-75 L IT:G |

|

IC SDRAM 128MBIT 133MHZ 54TSOP |

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

MT48LC8M16A2TG-75:G TR |

|

IC SDRAM 128MBIT 133MHZ 54TSOP |

Data Sheet |

|

|

||||||||||||||||||

|

MT48LC8M16A2TG-75:G |

|

IC SDRAM 128MBIT 133MHZ 54TSOP |

Data Sheet |

|

|

||||||||||||||||||

(China (Mainland))

(China (Mainland))